Подтяжка вообще вроде нам не нужна на вход.

Интересный код ,

Обязательно присобачу и допилю уарт управление, уж очень перспективно и круто, даже кнопочки не нужно будет клацать на донгле)

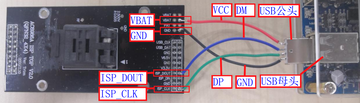

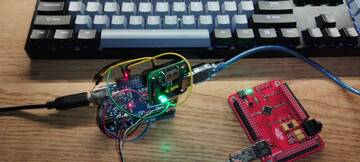

Также я опробовал вариант с проверкой подтяжки на D+, но там вроде есть проблема, что если вместе с атмегой к чипу я подвожу USB от компа, то всё работает, но если к атмеге подключен только чип, то ничего не работает.. Но в твоём коде вроде именно это и проверяется.

У меня оба варианта работают, наверно тупо от платформы зависит. Атмега деревянная просто). Но работает вроде идельно) Вот токо конченные дюпонты и провода бесят. Приходится просто спаивать норм проводами.

- Подпись автора

USMicro® 2026©