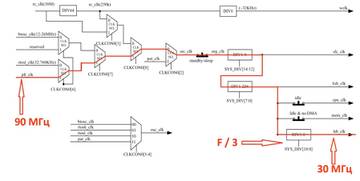

Тогда с настройками по умолчанию (из sdk) частота шины lsb должна быть 30 МГц. Вытащил из регистра SYS_DIV значение делителей через которые проходит тактовый сигнал от pll_sys_clk до lsb_clk. Оно оказалось равным 3. Таким образом, на входе pll_clk должно быть 90 МГц, как показано на картинке ниже. Но откуда берутся эти 90 МГц? Что не дели и как не умножай, ни от одного источника 90 мегагерц не получается.

P.S. На всякий случай проверил, не начудил ли я чего с настройками таймера. Включил тактирование Timer3 от кварцевого генератора bt_osc (период сигнала шим 1000), получил на частотомере 24 КГц ровно. Значит с таймером все нормально.