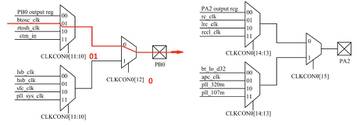

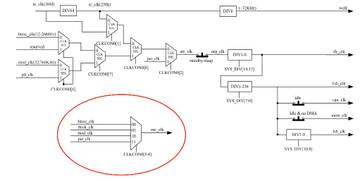

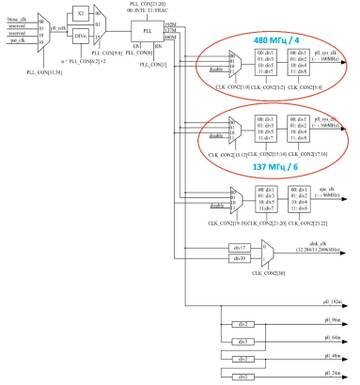

Приступил на днях к экспериментам с PLL чипов AC692x. Объектом исследований выбрал MH-M18, он же как будто AC6925D. Тут же потерпел фиаско на самом простом - вывод тактового сигнала на тестовый вывод. Что было бы полезно для контроля частоты синтезируемой PLL. Попытался завести сигнал с btosc_clk на порт PB0. Биты PB0_SEL выставлял по одному во избежание ошибок. Увы, ничего не шевелится, осцилл ничего не регистрирует на PB0 кроме наводок с соседних пинов. С выводом тактового с pll_sys_clk тоже глухо. На всякий случай проверил, не занят ли PB0 светодиодом или кнопками. AD-клавиатура обнаружилась, я ее перекинул на другой порт, но не помогло.

Вот так делал:

JL_CLOCK->CLK_CON0 &= ~BIT(12);

JL_CLOCK->CLK_CON0 &= ~BIT(11);

JL_CLOCK->CLK_CON0 |= BIT(10);