я в том смысле, что ты gdb запустил или просто вывод uart?

Под дебагом он имеет ввиду вывод отладочных строк через UART

- Подпись автора

水Mizu-DEC JLtech since 22.06.2019

USMI |

Привет, Гость! Войдите или зарегистрируйтесь.

Вы здесь » USMI » MCU, SoC, CPU Микроконтроллеры » JL SoC. 杰理芯片

я в том смысле, что ты gdb запустил или просто вывод uart?

Под дебагом он имеет ввиду вывод отладочных строк через UART

水Mizu-DEC JLtech since 22.06.2019

я в том смысле, что ты gdb запустил или просто вывод uart?

Конечно же уарт. Там со стороны чипа только он через printf.

USMicro® 2026©

О нормальном дебаге с остановкой на лету и отладкой можно забыть )

USMicro® 2026©

что так? вроде, в sdk встречается uboot.boot_debug, и даже скрипт запуска gdb run_jtag.sh, но куда это вставлять?

хотя, вот я у китайцев тоже не видел по этому поводу ничего. показуха с этим jtag.

Там есть эмулятор cJTAG через виртуальный комп порт, и через дебаг сервер на компе. Оно вроде только для прошивки и все, от туда и

run_jtag.sh

в sdk встречается uboot.boot_debug

Не везде он есть, кажись я видел его только раз). В SDK есть остатки от кода ПЛИС, там код судя по всему отрабатывают на FPGA.

USMicro® 2026©

Не везде он есть

в 5х, 6х sdk есть надо бы попробовать зашить его.

Конечно с таким хабом проблемы будут точно, так как он STT, и поэтому через него CH340 будет конфликтовать с чипом.

А поп подробнее можно про виды хабов? И почему будут проблемы?

USMicro® 2026©

Напоследок думаю можно ещё это проверить, главное тут между одной ногой с USB и пином (в данном случае это 10) поставить резистор на несколько кОм (я использовал на 5.1 кОм)

Не вышло.

Я уже собираю донгл))) устал дёргать проводочки

А поп подробнее можно про виды хабов? И почему будут проблемы?

Проблема в том, что чип после приёма ключа сначала пытается узнать частоту кварца, чтобы потом правильно настроить PLL и перейти к работе по USB.

Для этого он подтягивает D+ к питанию, потом уже ожидает импульсы на этой самой ноге, и по истечении некоторого времени (около секунды), подтяжка отключается и всё идёт заново.

Так как простой подтяжкой D+ нельзя просто так выйти на High-Speed (USB 2.0) шину, устройство определяется как Full-Speed устройство, поэтому оно подключается вместе к остальным Full/Low-speed (USB 1.1) устройствам на шине (типо клавы/мыши, CH340 и т.п.), и поэтому разговор далее идёт именно про USB 1.1.

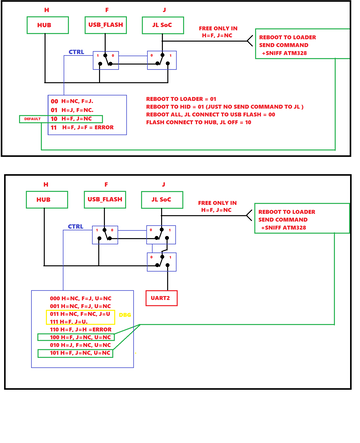

У USB 2.0 хабов существует два вида организации TT: STT (Single Transaction Translator) и MTT (Multiple Transaction Translator).

У STT хабов на все порты есть только один TT, поэтому все USB 1.1 устройства делят одну шину, и принцип получается как с USB 1.1 хабами.

Но у MTT хабов на каждом порту уже стоит по своему TT, поэтому каждое устройство имеет свою отдельную шину, которая независима от других устройств.

USB хабы сами по себе устроены так, что когда хост хочет что-то отправить на определённое устройство, хаб отсылает это на все устройства, которые к нему подключены, а ответ уже отсылается обратным путём напрямую к хосту.

Если например использовать USB 1.1 хаб, или STT USB 2.0 хаб, то можно будет наблюдать такой эффект:

Например если в хаб воткнуть CH340 и чип JL, то те пакеты которые идут к CH340, например данные для отправки по UART или запросы на наличие принятых данных, будут также просачиваться к шине где сидит JL чип, или если например JL будет в режиме аудиокарты, и туда передавать звук, то на шине у CH340 можно будет увидеть пакеты с аудио для JL.

Именно это и мешает определению частоты кварца чипом, ибо весь этот шум может либо не привести ни к чему, либо приведёт к неверному определению частоты и, как следствие, к неверным частотам для USB (а то и для всего чипа) и дальнейшой невозможности общения с компом, и всем этим проблемам с определениям устройств, так как приём этих самых SOF пакетов устроен очень примитивно, при помощи захвата таймером ноги D+, понятное дело что таким образом узнать PID у пакета будет невозможно, и как следствие, отличать SOF-ы от других пакетов.

Отредактировано kagaimiq (2023-12-29 03:00:10)

水Mizu-DEC JLtech since 22.06.2019

Hi, I was wondering if you could take a look at my AC6969A2 dump.

https://drive.google.com/file/d/1AoQMSO … sp=sharing

I followed the instructions in this post ( JL SoC. 杰理芯片 )

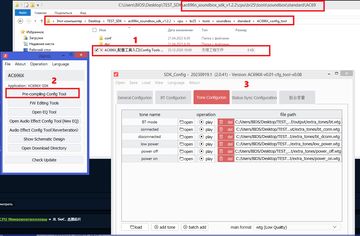

My app_area_head section only has app.bin. It doesn't have cfg_tool.bin like in the screenshot.

My tone section only has index.idx, bt_conn.wtg bt_dconn.wtg, low_power.wtg, bt.wtg. It does not contain the lines bt.mp3, power_off.wtg, linein.mp3, music.mp3, pc.wtg, as in the screenshot.

Where should I look for uboot.boot and cfg_tool.bin?

Is there a wtg to mp3 converter and mp3 to wtg converter that I can use?

Thank you

Я нашел ссылку на cfg_tool.bin после раздела tone, однако адреса, похоже, неверны.

от 0x20 до 0x3B9, конец не содержит FFFFFFF, как в других файлах.

Мне пока не удалось найти файл uboot.

Файлы wtg, похоже, находятся в сжатом формате mp3, поскольку они содержат одно и то же имя. Например. bt.mp3 или bt.wtg. Мой чип содержит только файлы wtg, потому что у него меньше памяти. Интересно, есть ли у JieLiконвертер mp3 в wtg?

😊

Всё это логично. Но про кварц, не понятно? Зачем оно пытается узнать ? Может ты имел ввиду просто тактирование некоторых чипов от донгла ?

А ты не пробовал повесить ардуинку и чип через хаб? У них же вроде разные vid/pid/id. Да у самого концентратора один vid/pid/id -но вет у конечных устройств оно разное.

как следствие, к неверным частотам для USB (а то и для всего чипа) и дальнейшой невозможности общения с компом, и всем этим проблемам с определениям устройств, так как приём этих самых SOF пакетов устроен очень примитивно, при помощи захвата таймером ноги D+, понятное дело что таким образом узнать PID у пакета будет невозможно, и как следствие, отличать SOF-ы от других пакетов.

А я думал что там просто тип и скорость определяется подтяжкой и все).

USB хабы сами по себе устроены так, что когда хост хочет что-то отправить на определённое устройство, хаб отсылает это на все устройства, которые к нему подключены, а ответ уже отсылается обратным путём напрямую к хосту.

Нужно это посмотреть на ослике.

USMicro® 2026©

Файлы wtg, похоже, находятся в сжатом формате mp3, поскольку они содержат одно и то же имя. Например. bt.mp3 или bt.wtg. Мой чип содержит только файлы wtg, потому что у него меньше памяти. Интересно, есть ли у JieLiконвертер mp3 в wtg?

Извините, я не занимался еще заменой звуков, занят платами)

Но вот то что вам вроде нужно.

第二步:包管理工具的安装

包管理工具,是用于下载杰理SDK需要使用的工具,同时也负责打开 “.jlxproj” 后缀的文件。即,包管理工具负责从杰理服务器端,把SDK所需要的最新工具,下载到当前电脑。

(包管理工具下载路径:http://jl-update.oss-cn-shenzhen.aliyuncs.com/jieli-pkgman-setup-latest.exe)

双击 “latest.exe” 进行安装,按照提示安装完成即可,安装完成后,双击直接打开后缀为 “.jlxproj” 的文件。

https://test03.jieliapp.com/PublicDoc/AC63N/html/DST/第 1 章 快速入门.html

USMicro® 2026©

Но про кварц, не понятно? Зачем оно пытается узнать ?

Ну, они посчитали, что лучше определять частоту на лету, вместо того, чтобы хардкодить частоту скажем в 24 МГц.

Тем более, что в некоторых ситуациях частота может быть и не 24 МГц совсем, например при тактировании от LRC.

Понятное дело, что для того, чтобы из PLL выходила нужная частота, нужно знать какая у него опорная частота, чтобы потом соответствующим образом подстроить его делители.

У них же вроде разные vid/pid/id. Да у самого концентратора один vid/pid/id -но вет у конечных устройств оно разное.

Это ни на что не влияет, проблема не в софте, а в железе.

А я думал что там просто тип и скорость определяется подтяжкой и все).

Подтяжкой можно различить только между Low-speed и Full/High-speed устройствами, собственно для попадания на High-speed нужно сделать дополнительное согласование, потом эта подтяжка вообще отлючается, т.к. тут уже линии нагружаются иначе.

水Mizu-DEC JLtech since 22.06.2019

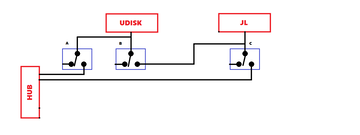

Вот, вторая пара ключей, и третья , но вопрос, а стоит оно того?

Во первых сам стандарт усб - подразумевает что выводы питания всегда подключаются первыми, а потом дата. Тоесть порт усб флешки тоже лучше подключить через тот же мосфет что и JL, во избежание зависаний и тд.

Это все не проблема, тайминги проставить. + каждая пара ключей должна иметь свой канал управления, ведь на одной ноге можно только 1 или 0.

Во вторых вроде как одно свободное положение остается для отправки команд чипу JL.

Во третьих - а как уарт коммутировать то? Я щас вожусь с этим.

Получается слишком много комплектухи, хаб, 6 ключей, два уарта.

Все таки остановлюсь тупо на варианте где JL подключается или к хабу или к флешке.

И с одним уартом, ну да - придется два джампера установить.

Оно явно не стоит того что бы так запариваться. Главное тупо донгл с ключами для хаба. Простота и надежность. Максимум - управление по уарту. Но тогда нужна микра хаба. Можно отказаться и от этого, тогда только тупог переводилка в бут.

USMicro® 2026©

Ну короче, проверил, с одной парой ключей.

Так как атмега и JL всегда подключены, то ключи стоят от JL до хаба, или до флешки. Что бы перевести в бутлоадер - нужно отключиться от хаба (ну только из за этого мне нужны ключи, что бы не слать всякую фигню на хаб.) - а так как ключи переключают только, у них состояние или подключено одно или другое, (так мы коммутируем чип с компом или с флешкой), то когда мы переводим в бут, то автоматом отключаем хаб, и подключаем флешку, (или одно или другое, хаб отлетает сразу, остается флешка), думал что воткнутая флешка будет мешать переводить в бутлоадер. А вот и нет, работает все с параллельно воткнутой флешкой, пусть оно шлет на флешку хлам вместо хаба, пофигу, да и осликом ткнул - ну даже секунды нету сигнала на ножках. Зато с донгла можно переключаться , проверил 3 режима, перевод в бутлоадер, включение и подключение флешки (в сдк должен быть автостарт подключенных устройств, мы не эмулируем подключение усб, это что бы не нарушать работу сдк) и включение чипа и подключение в роли аудиокарты/усб устройства.

Работает все с всунутой флешкой, не шлет мусор на хаб, переводит в бут, в аудиокарту, включает само флешку к чипу. Вообщем доволен.

И при этом главное - один раз воткнул все и всё. никаких перетыканий ручками.

Проверил работу уарта на ардуине, для прошивки ардуины нужны обязательно оба контакта RX-TX , сделаем просто - джамперы на усб от уарта, мы же не всегда собираемся дебажить черех узб порты?), Зато просто в реализации, нету кучи коммутаторов, софтового уарта на атмеге, и JL можно вешать параллельно уарту CH340, управлению это не мешает.

Осталось присобачить управление донглом по уарту. И протестировать, и это уже завтра)

USMicro® 2026©

А вот это уже интересно, какие новшества в схеме?

Я проектирую макетку, пока не паял, чтобы добавить.

Или это ты не с донглом работаешь?

Отредактировано priradio585 (2023-12-30 10:07:11)

И как я понял АВ - на 4 мегабайта флешки

по моему, он без флеша. нужно внешнюю вешать.

Ну короче, проверил, с одной парой ключей.

Уже нифига не работает, переткнул в усб 2.0 и все накрылось, флешка мешает.

Короче сидел искал ключи какие то , что бы в одном корпусе было два канала 1:4, есть всякое интересное, причем с hight-z состоянием, тоесть не только куда то подключено, а и еще "подвешенное состояние", это то что нужно, но они дорогие, и самое главное ни где не найти, например на алике. Так что будем лепить из чего есть..

Нам нужно состояние - когда устройство ни куда не подключено, короче будем юзать на одно устройство одну пару ключей,

Так подходит, пофиг на ключи, они дешевые, зато это уже точно работает как нужно.

USMicro® 2026©

CD4016 не подойдёт?

Вы здесь » USMI » MCU, SoC, CPU Микроконтроллеры » JL SoC. 杰理芯片